實習生公開在 Backbone 在商業開發部的實習日常:親身體驗人體工學專案開發|工作甘苦談

無論你正面臨面試挑戰,或是在職場中努力站穩腳步,這裡整理了實用經驗與建議,協助你釐清方向、提升應對力,並在每個職涯轉折點做出更明智的選擇。

![]() 文章目錄

文章目錄

文/Kelly Huang

距離實習結束也快半個月,這半年中遇到了很多美好的人事物,工作上有挑戰、有成就感、當然也有遇到瓶頸的時候。想好好整理這段時間以來的收穫與想法,提筆紀錄這趟奇妙的實習之旅!

▲實習生公開在 Backbone 在商業開發部的實習日常

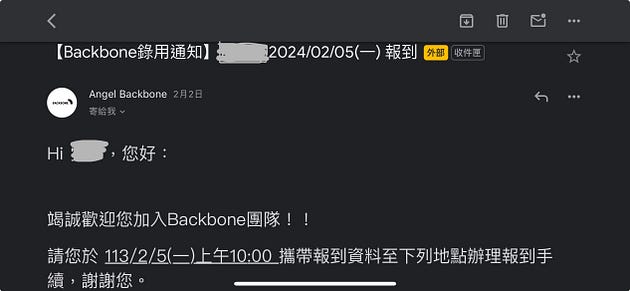

為什麼會去 Backbone?如何拿到這份實習 Offer?

很多朋友都是資工宅宅 XD 很重視工作設備,從滑鼠、鍵盤(甚至連鍵帽)、螢幕都超級講究。某天講到椅子的時候,他們開始跟我分享自己的椅子雖然有點貴,但一張好椅子是對自己健康的投資、有多好坐、有很多功能可以調來調去、是台灣很有名的品牌 bala bala 的。但當時對椅子沒有研究的我,根本沒有聽過(我很抱歉><)但卻稍稍對這個品牌留下印象。

後來偶然回社團聽學長姊分享,意外發現那天分享的創社元老之一正是 Backbone 的創辦人 — 家葳,來分享創業經驗、品牌轉型的主題。我超驚訝立馬跟朋友分享(超荒謬但很巧)。

大三上看到身旁朋友們開始準備研究所、實習、做專案,在 peer pressure 下覺得自己也該找份實習,加上我對外交系本科的內容確實不太感興趣,也想著或許可以透過實習與職場接軌,藉此釐清自己想要的到底是什麼。剛好在校內的新創博覽會,遇到 Backbone 外銷部的主管聊了蠻多他也鼓勵我,若有興趣可以寄履歷到他們公司。所以 我 就 投 了!

後來家葳約了 1 on 1 的面談時間,想了解我的實習目標及公司能如何安排,希望能讓我有個充實的實習體驗(這很重要!有被重視的感覺)。過程中除了公司的介紹、旗下各品牌特色,較多篇幅是著重在討論我想要做的職位,當時我稍微列了商業開發、PM、行銷。沒多久後就正式收到外銷部商業開發的實習生 Offer 啦 🎉

實習生的一天在做什麼?

由於還有學校課業,我一周只會進公司三天。早上進公司後會先處理 Wavebone 美國倉庫的出貨、看 support 信箱、回覆客戶訊息。每周一早上會開外銷部例會,主要是 follow up 各業務的開發進度、業助負責的海運時間、交期等等,及若遇到較棘手的客戶該如何回覆等等。

中午是我最期待的時間🤩 大家會一起吃午餐,無論是早餐日、羊肉便當(這個我真的吃不懂)、自助餐、福園、燒臘等等,都是我的心頭好!一起買飯也算是另類的 team building 吧?

午休後一直到下班,主要工作內容是尋找並建立潛在客戶名單,撰寫並寄出開發信件,回潛在客戶對產品的相關問題及討論後續合作方式。有時也會負責做些產品較 routine 的基礎建設 (? 像是商品的貨號表格、品牌介紹簡報、說明書翻譯、報價單等等;雙周會寫個 Linkedin 品牌貼文、找圖片素材。

▲工作內容之一的小任務

我在這份實習的三大 Takeaways

Taking fully ownership

在這份工作中雖然掛的是實習生的身分,但工作內容、員工福利與正職是沒有差別的。主管也非常願意放手,從 reach 客戶、撰寫開發信、和客戶溝通後續合作方式、與其他部門主管開會,全部都是我直接經手。後續進入其他公司擔任實習生後,才更發現這件事情有多難能可貴😭 大部分公司的實習生都是小小螺絲釘,從事流動率最高、最 routine 的工作,很少有機會直接碰到這些內容。

最印象深刻的是,在實習的尾聲,偶然談到一個韓國高階客戶對我們很有興趣(不枉費我平常聽很多 KPOP 音樂)從第一封 cold mail、寄報價單、討論樣品寄送到開線上會議,全部都是我一手包辦,前後來回費時將近一個多月,但整個過程下來有滿滿的成就感 💖 原來自己有能力談到一個客戶!

▲人生中第一次開商業會議!超緊張!

Keep learning! Keep growing!

在開發前因為對 cold mail 的架構不太熟悉,大量看了很多相關文章及教學(超推 Partick Dang!)也透過線上資源找出更多"實用開發工具"和鑽研"文書軟體"更多強大功能。針對經營公司各品牌的 Linkedin 小專案也讀了些 SEO 優化、社群經營的相關內容。遇到工作瓶頸時更是聽了很多 podcast 上前輩們的分享和相關書籍。

而實習中段時對工作更熟悉,除了繼續深入外也對其他領域產生興趣。幸運的是,我的 Mentor 也非常支持我,了解我的想法後更願意讓我參與其他 side projects,像是協助新電商渠道的合作與建置、經營品牌官方 Linkedin、到北流協助新品拍攝工作、參與整合行銷部的內訓等等。這些挑戰都是成長的機會,也讓我在半年內快速接觸到不同領域且有實體成果能分享,這點我在日後面試不同實習缺時更能深刻感受到!相較於其他實習工作都是偏行政雜事,面試官在問到關於工作很細節的問題時,我都能侃侃而談,並能從容且流暢的從當時面臨的情況、我做了什麼、達到什麼成果,一路到有什麼反饋與收穫,完全不會被問倒(投入程度、在專案中有多少 ownership,面試時很容易就看得出來 )。

▲新品拍攝日,看到超多貴貴的設備

Work hard, laugh harder

我覺得在剛接觸職場初期能體驗到健康的環境對日後非常有幫助,能更清楚未來想要的工作氛圍、工作型態、職場文化等。Backbone 團隊成員的年齡相近,除了認真工作時間,辦公室的氣氛都很歡樂🤣 (聊天時常會出現一些莫名其妙爛梗、荒謬的對話,我真的會笑死)此外,扁平化的組織架構也讓我在跟主管溝通時更順暢且更願意表達想法!不定時的聚餐唱歌也超好玩,大家都很瘋,絕對是正向 team building🎉

▲天使同事們 ~

後記

在這段實習中雖然時間說長不長、說短不短,但卻能一瞥整個製造業的產業鏈中原來有這麼多不同的部門在各司其職,從製造商、海運到業務、行銷等職位,原來一件家具能送到手上是整個龐大產業結構運作下的成果,想想還真是不可思議。

另外也感受到「主動」在工作中的重要性,無論是主動爭取機會、表達自己的需求、展現自己的能力,這些行動都在不斷提升他人對自己能力的評估,也影響到他們是否願意將任務交給你。

不要總是等別人告訴你,而是提前預判下一步。

在此也非常感謝在公司遇到的各位夥伴,總是細心回答我許多問題,幫我的腦袋擴充了不少專有名詞和產業知識,給了我一份美好的實習體驗並培養足夠的能力繼續往下個挑戰出發!

※本文由 Kelly Huang 授權勿任意轉載,原文《實習心得分享|我在人體工學領導品牌 Backbone,擔任商業開發實習生的日子》